串行通信协议(I2C、SPI、UART、SCCB、CAN)

推荐一部书,在这本书里面详细介绍了I2C、SPI、UART和CAN等通信协议,写的蛮不错的。

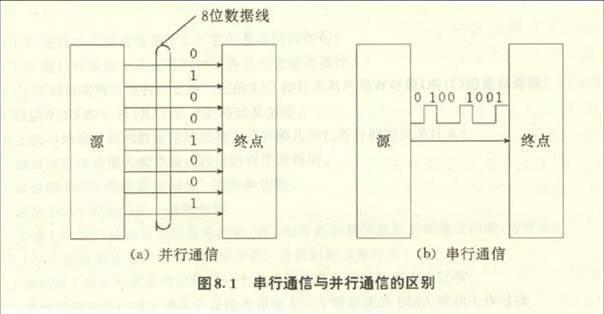

串行通信:设备与设备之间,传输数据按顺序依次1bit位接1bit位进行传输。

并行通信:设备与设备之间,通过多条传输线,可以同时传输多个bit位的信号。

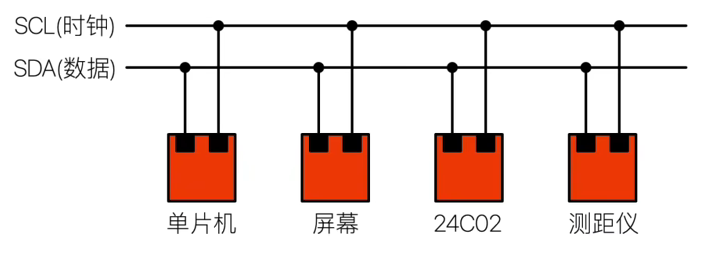

I2C(Inter-Integrated Circuit)

1.简单的双向两线制总线协议标准、半双工通信

2.双向串行数据线(SDA)用来表示数据,串行时钟线(SCL)用于数据收发同步

3.总线通过上拉电阻接到电源。当I2C 设备空闲时,会输出高阻态,而当所有设备都空闲,都输出高阻态时,由上拉电阻把总线拉成高电平。

写数据

- 开始数据传输后,先发送一个起始位(S),主设备发送一个地址数据(由7bit的从设备地址,和最低位的

写标志位组成的8bit字节数据,该读写标志位决定数据的传输方向),然后,主设备释放SDA线,并等待从设备的应答信号(ACK)。- 从设备应答主设备后(表示有这个从设备存在),主设备再发送要读取的寄存器地址,从设备应答主设备(ACK),表示设备内有这个地址。

- 当写数据的时候,Master每发送完8个数据位,Slave设备如果还有空间接受下一个字节应该回答“ACK”,Slave设备如果没有空间接受更多的字节应该回答“NACK”,Master当收到“NACK”或者一定时间之后没收到任何数据将视为超时,此时Master放弃数据传送,发送“Stop”。

读数据

- 开始通讯时,主设备先发送一个起始信号(S),主设备发送一个地址数据(由7bit的从设备地址,和最低位的

写标志位组成的8bit字节数据),然后,主设备释放SDA线,并等待从设备的应答信号(ACK)。- 从设备应答主设备后(表示有这个从设备存在),主设备再发送要读取的寄存器地址,从设备应答主设备(ACK),表示设备内有这个地址。

- 主设备再次发送起始信号(S),主设备发送设备地址(包含

读标志),从设备应答主设备,并将该寄存器的值发送给主设备。- Slave设备每发送完8个数据位,如果Master希望继续读下一个字节,Master应该回答“ACK”以提示Slave准备下一个数据,如果Master不希望读取更多字节,Master应该回答“NACK”以提示Slave设备准备接收Stop信号。

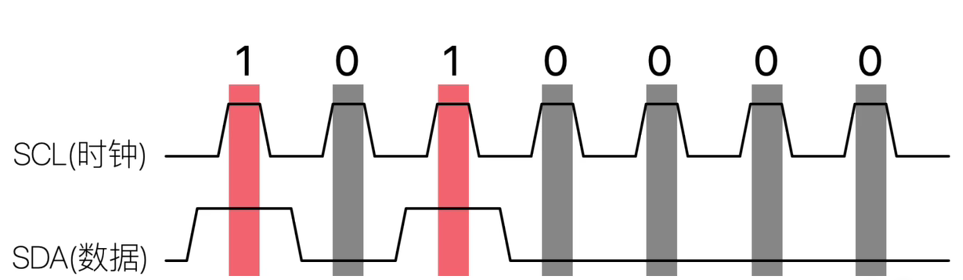

起始信号和停止信号

SCL处于高电平时,SDA由高到低变化,这种信号是起始信号

SCL处于高电平,SDA由低到高变化,这种信号是停止信号

数据的有效性

在数据传输期间(不包括起始信号和停止信号),I2C协议对数据的采样发生在SCL高电平期间。SCL为高电平时,SDA必须保持稳定,不允许改变,在SCL低电平时才可以进行变化。

应答信号

I2C数据以字节(即8bits)为单位传输,每个字节传输完后都会有一个ACK应答信号。应答信号的时钟是由主设备产生的。主机需要释放SDA总线,把总线控制权交给从机,由于上拉电阻的作用,此时为高电平。

- 应答(ACK):拉低SDA线,并在SCL为高电平期间保持SDA线为

低电平 - 非应答(NOACK):不要拉低SDA线(此时SDA线为高电平),并在SCL为高电平期间保持SDA线为

高电平

速率

- 标准模式(Standard):100kbps

- 快速模式(Fast):400kbps

- 快速模式+(Fast-Plus):1Mbps

- 高速模式(High-speed):3.4Mbps

- 超快模式(Ultra-Fast):5Mbps(单向传输)

实现

- I2C总线协议的软件模拟实现方法–单片机

- Linux内核中I2C模块的实现方法

SPI(Serial Peripheral interface)

全双工数据传输、没有规定最大传输速率、没有地址方案、也没规定通信应答机制

- MISO(Master input slave output): 主设备输入/从设备输出引脚。该引脚在从模式下发送数据,在主模式下接收数据。

- MOSI(Master output slave input): 主设备输出/从设备输入引脚。该引脚在主模式下发送数据,在从模式下接收数据。

- SCLK(Serial Clock):串行时钟信号,由主设备产生。

- CS/SS(Chip Select / Slave Select):从设备片选信号,由主设备控制。它的功能是用来作为“片选引脚”,也就是选择指定的从设备,让主设备可以单独地与特定从设备通讯,避免数据线上的冲突。

SPI数据发送接收

对主设备的SPI模式进行配置,通过配置时钟极性和相位设置主设备的通信模式,决定读取数据的方式,比如信号上升沿读取数据还是信号下降沿读取数据;

时钟极性 CKP/Clock Polarity/CPOL

- CPOL=0:时钟空闲SCLK=0;

- CPOL=1:时钟空闲SCLK=1;

时钟相位 CKE /Clock Phase (Edge)/CPHA

CPHA=0:在时钟的第1个跳变沿(上升沿或下降沿)进行数据采样,在第2个跳变沿(上升沿或下降沿)数据发送CPHA=1:在时钟的第1个跳变沿(上升沿或下降沿)进行数据发送,在第2个跳变沿(上升沿或下降沿)数据采样

4种模式

-

CPOL=0,CPHA=0:此时空闲态时,SCLK处于低电平,数据采样是在第1个边沿,也就是SCLK由低电平到高电平的跳变,即数据采样在上升沿,数据发送是在下降沿。 -

CPOL=0,CPHA=1:此时空闲态时,SCLK处于低电平,数据发送是在第1个边沿,也就是SCLK由低电平到高电平的跳变,即数据发送是在上升沿,数据采样是在下降沿。 -

CPOL=1,CPHA=0:此时空闲态时,SCLK处于高电平,数据采样是在第1个边沿,也就是SCLK由高电平到低电平的跳变,即数据采样在下降沿,数据发送在上升沿。 -

CPOL=1,CPHA=1:此时空闲态时,SCLK处于高电平,数据发送是在第1个边沿,也就是SCLK由高电平到低电平的跳变,即数据发送是在下降沿,数据采样在上升沿。

通信过程

- 拉低对应SS信号线,表示与该设备进行通信

- 主机(Master)将要发送的数据写到发送数据缓存区,缓存区经过移位寄存器(0~7),串行移位寄存器通过MOSI信号线将字节一位一位的移出去传送给从机,从机的MISO接口接收到的数据经过移位寄存器一位一位的移到接收缓存区。

- 从机(Slave)也将自己的串行移位寄存器(0~7)中的内容通过MISO信号线返回给主机。

参考

UART

通用异步收发器(Universal Asynchronous Receiver/Transmitter),通常称作UART,是一种串行、异步、全双工的通信协议。

通信协议

数据包由起始位、数据帧、奇偶校验位和停止位组成。

起始位

当不传输数据时,UART数据传输线通常保持高电压电平。

若要开始数据传输,发送UART会将传输线从高电平拉到低电平并保持1个时钟周期。当接收UART检测到高到低电压跃迁时,便开始以波特率对应的频率读取数据帧中的位。

数据帧

数据帧包含所传输的实际数据。

如果使用奇偶校验位,数据帧长度可以是5位到8位。

如果不使用奇偶校验位,数据帧长度可以是9位。

在大多数情况下,数据以最低有效位优先方式发送。

奇偶校验

- 奇校验(odd parity):如果数据位中’1’的数目是偶数,则校验位为’1’,如果’1’的数目是奇数,校验位为’0’。

- 偶校验(even parity):如果数据为中’1’的数目是偶数,则校验位为’0’,如果为奇数,校验位为’1’。

停止位

为了表示数据包结束,发送UART将数据传输线从低电压驱动到高电压并保持1到2位时间。

参考

波特率

数据传输速率使用波特率来表示,单位bps(bits per second)。

9600bps:传输一个比特需要的时间是1/9600≈104.2us。

SCCB

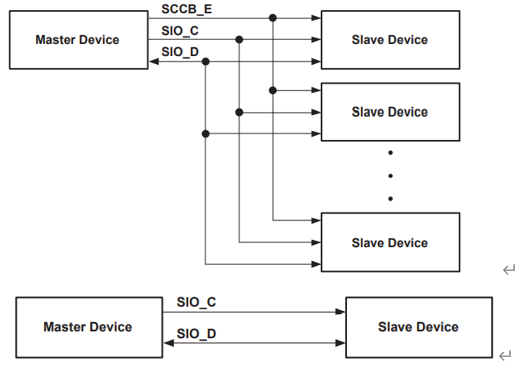

Serial Camera Control Bus,串行摄像头控制总线,有两种工作模式,一主多从,一主一从模式。一主多从,即3线操作;一主一从,即2线操作。

通信协议

CAN

控制器局域网总线(CAN,Controller Area Network)是一种用于实时应用的串行通讯协议总线,它可以使用双绞线来传输信号,是世界上应用最广泛的现场总线之一。详细了解CAN协议可以查看国际标准(ISO11519以及ISO11898)。

CAN 总线协议已经成为汽车计算机控制系统和嵌入式工业控制局域网的标准总线,同时CAN作为底层协议为大型货车和重工机械车辆设计了SAE J1939等协议。

闭环总线网络

ISO11898 标准的高速、短距离“闭环网络”

开环总线网络

ISO11519-2 标准的低速、远距离“开环网络”

差分信号

使用差分信号传输时,需要两根信号线(CAN_High和CAN_Low),通过两根信号线的电压差值来表示逻辑 0 和逻辑 1。

- 抗干扰能力强

- 双绞线,抑制它对外部的电磁干扰

假设这两个信号线的振幅相等、相位相反,双绞线受到干扰后,电压变化,但电压差值不变:

CAN 协议中的差分信号:

在CAN总线的规范中,将二进制位

0定义为显性位或显性信号/电平,1定义为隐性位或隐性信号/电平。

根据图中的

典型值来分析,对于ISO11898(高速)来说,表示逻辑 1时 (隐性电平) ,CAN_High和CAN_Low线上的电压均为2.5v,即它们的电压差为0V;而表示逻辑 0时 (显性电平) ,CAN_High的电平为3.5V,CAN_Low线的电平为1.5V,即它们的电压差为2V。

对于ISO11519-2(低速)来说,表示逻辑 1时 (隐性电平) ,CAN_High线上的电压为1.75v,CAN_Low线上的电压为3.25v,即它们的电压差为-1.5V;而表示逻辑 0时 (显性电平) ,CAN_High的电平为4.0V,CAN_Low线的电平为1.0V,即它们的电压差为3V。

CAN总线的

空闲状态或接收状态是逻辑1(隐性电平),电压差为0V(ISO11898)或者-1.5V(ISO11519-2),电压差低于逻辑0(显性电平)的电压差。

当多个设备争抢总线时,传输数据中的

隐性位‘1’被显性位‘0’覆盖,仲裁会利用这个特性。

由于 CAN 总线协议的物理层只有

1 对差分线,在一个时刻只能表示一个信号,所以对通讯节点来说,CAN 通讯是半双工的,收发数据需要分时进行。

通信协议

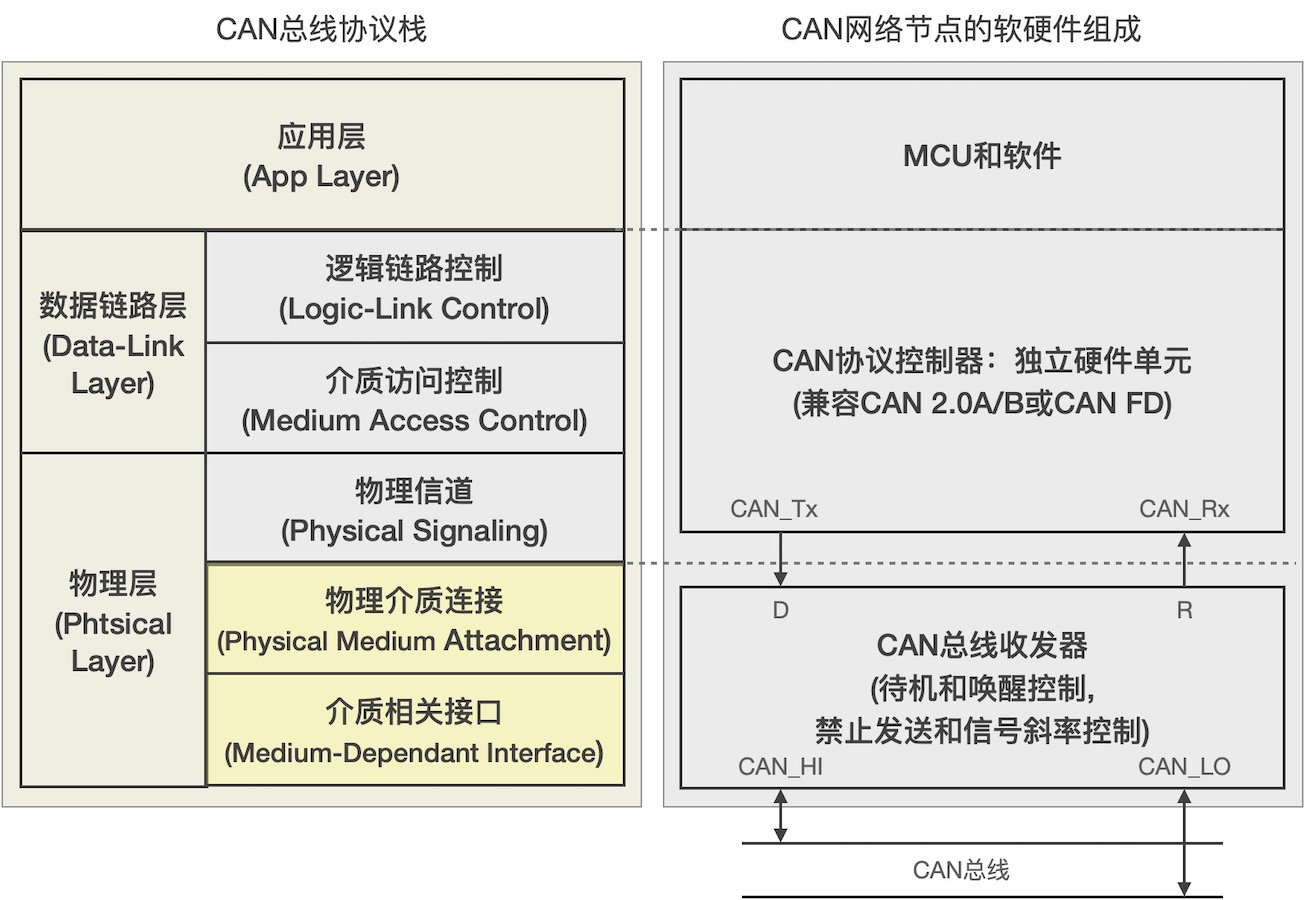

CAN 协议涵盖了 ISO 规定的 OSI基本参照模型中的数据链路层及物理层。

数据链路层分为

MAC子层和LLC子层,MAC 子层是 CAN 协议的核心部分。数据链路层的功能是将物理层收到的信号组织成有意义的消息,并提供传送错误控制等传输控制的流程。具体地说,就是消息的帧化、仲裁、应答、错误的检测或报告。

数据链路层的功能通常在 CAN 控制器的硬件中执行。多主或无主网络架构的CAN总线节点对总线占用权的竞争和仲裁方案通常采用CSMA/CA,即载波侦听多路访问/碰撞避免,这点在计算机网络学过,忘记了可以复习一下。

CAN总线是一种多主网络架构,

每个CAN节点的数据信息被系统设计和维护者分配惟一的ID,CAN总线收发器允许CAN协议控制器监测网络状态,任何时候任何节点都可以主动地将节点的数据信息和对应的惟一ID封装成数据帧并启动消息发送, 该发送过程是否成功将取决于总线状态和总线竞争的仲裁结果,如果发送失败(抢占总线失败或收到发送错误帧)则CAN协议控制器将通过重试机制再次发送。

CAN总线收发器不仅具有

差分驱动和差分接收能力,还具有收发环路,即发送的同时还支持接收。在原理上收发环路允许CAN总线节点的CAN协议控制器能够侦测每一个数据位是否发送成功。

CAN协议定义了5种类型的帧,分别为

- 数据帧

- 遥控帧

- 错误帧

- 过载帧

- 帧间隔

另外,数据帧和遥控帧有标准格式和扩展格式两种格式。标准格式有 11 个位的标识符(Identifier: 以下称 ID),扩展格式有 29 个位的 ID。

帧的用途如下:

数据帧

(1) 帧起始(标准、扩展格式相同)

表示帧开始的段。1 个位的显性位。

- 显性电平的逻辑值为“0”,隐性电平为“1”。

- “显性”具有“优先”的意味

(2) 仲裁段

表示数据的优先级的段。标准格式和扩展格式在此的构成有所不同。标准格式的 ID 有 11 个位,扩展格式的 ID 有 29 个位。

(3) 控制段

控制段由 6 个位构成,表示数据段的字节数。标准格式和扩展格式的构成有所不同。

- 保留位(r0、r1)

- 保留位必须全部以显性电平发送。但接收方可以接收显性、隐性及其任意组合的电平。

- 数据长度码(DLC)

- 数据长度码与数据的字节数的对应关系如表所示。

数据的字节数必须为 0~8 字节。但接收方对 DLC = 9~15 的情况并不视为错误。

(4) 数据段(标准、扩展格式相同)

数据段可包含 0~8 个字节的数据。从 MSB(最高位)开始输出。

- 数据长度码与数据的字节数的对应关系如表所示。

(5) CRC 段(标准/扩展格式相同)

CRC 段是检查帧传输错误的帧。由 15 个位的 CRC 和 1 个位的 CRC 界定符(用于分隔的位)构成。

CRC 的计算范围包括帧起始、仲裁段、控制段、数据

段。

(6) ACK 段

ACK 段用来确认是否正常接收。由 ACK 槽(ACK Slot)和 ACK 界定符 2 个位构成。

- 发送单元的 ACK 段

- 发送单元在 ACK 段发送 2 个位的

隐性位。

- 发送单元在 ACK 段发送 2 个位的

- 接收单元的 ACK 段

- 接收到正确消息的单元在 ACK 槽(ACK Slot)发送

显性位,通知发送单元正常接收结束。这称作“发送 ACK”或者“返回 ACK”。

- 接收到正确消息的单元在 ACK 槽(ACK Slot)发送

(7) 帧结束

帧结束是表示该该帧的结束的段。由 7 个位的隐性位构成。

参考