MicroBlaze系列教程(1):AXI_GPIO的使用

创始人

2024-05-21 02:39:44

文章目录

- @[toc]

- 简介

- 常用函数

- 使用示例

- 参考资料

- 工程下载

- @[toc]

- 简介

- 常用函数

- 使用示例

- 参考资料

- 工程下载

本文是Xilinx MicroBlaze系列教程的第1篇文章。

简介

AXI GPIO是基于AXI-lite总线的一个通用输入输出IP核,可配置为一个或两个通道,每个通道32位,每一位可以通过SDK动态配置成输入或输出方向,支持中断请求,配合中断控制器IP可实现外部中断触发。

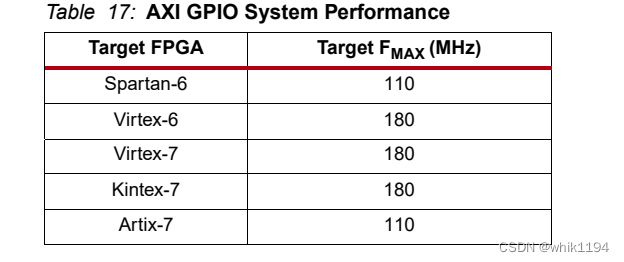

不同系列FPGA所支持的最高频率:

官方使用示例:

- xgpio_intr_tapp_example.c

- xgpio_example.c

- xgpio_intr_example.c

- xgpio_low_level_example.

相关内容

热门资讯

最新或2023(历届)关于铁人...

王进喜,1923年10月8日出生于甘肃省玉门县赤金堡一个贫苦的农民家庭。6岁讨饭,10岁给地主放牛,...

最新或2023(历届)森林防火...

森林防火须知手抄报图片

原创 半...

朝方突然甩出一份声明,把刚有点缓和苗头的半岛,一脚踹回了紧张模式。 2025新年钟声才敲响几天,...