【FLASH存储器系列十】Nand Flash芯片使用指导之一

目录

1.1 芯片简介

1.2 功能框图

1.3 存储结构

1.4 信号定义

1.5 双平面(plane)操作

1.6 Die间交错操作

1.7 错误管理

今天以MT29F8G08AJADAWP芯片为例,说明nand flash的操作方法。

1.1 芯片简介

这是一款镁光的容量8Gb,总线位宽8位的SLC NAND Flash,兼容ONFI 1.0标准。芯片内包含两个die,每个die为4Gb,每个die有两个plane,每个plane为2Gb,每个plane有2048个block,每个block为128K,每个block有64个page,每个page为2K,以上容量不包含每页用来存储坏块信息和ECC信息的spare area。

1.2 功能框图

1、I/O control:数据、命令、地址的输入输出口;

2、Status Register:片内的状态寄存器;

3、Command Register:命令锁存寄存器;

4、Address Register:地址由地址寄存器锁存并发送到行解码器以选择行地址,或发送到列解码器以选择列地址;

5、Control Logic:解码总线状态,判断当前属于地址输入、命令输入、或是数据输入输出周期;

6、存储阵列:两个plane,上图仅为芯片其中一个die;

7、Row decode:行地址解码;

8、column decode:列地址解码;

9、Data register:数据寄存器;

10、Cache register:缓存寄存器;

11、ECC:进行数据校验。

注意:数据寄存器和缓存寄存器可以单独操作,在缓存操作命令下,如页缓存读、页缓存编程,可以提升数据吞吐量。这个和CPU的cahe原理是一样的。

1.3 存储结构

Die、plane、Block、page前文已经说明,大家对照下图可以清晰地明白,不再赘述。这里说明一下每个plane上的数据寄存器和缓存寄存器,普通的页编程、页读取不需要经过数据寄存器,外部结构通过缓存寄存器直接和存储阵列交互。但是外部接口速率和存储阵列的读写速率相对较慢,以编程操作为例,如果要等外部数据全部输入进缓存寄存器,再由缓存寄存器往存储阵列里写,耗时较长,这时增加一个数据寄存器,在外部数据全部输入进缓存寄存器后,将数据拷贝到数据寄存器,然后在数据寄存器往存储阵列写数据期间,外部接口可以开启下一页数据往缓存寄存器里写,如此反复,则可以提升数据吞吐量。

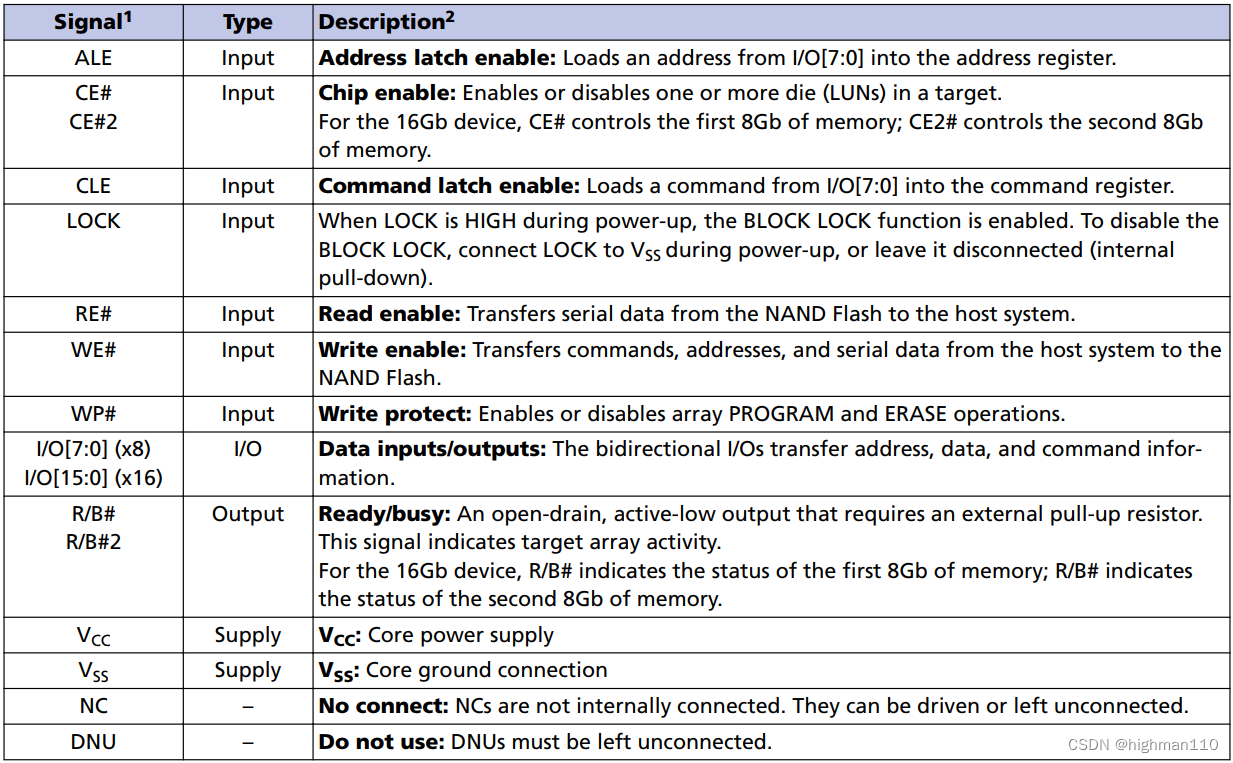

1.4 信号定义

信号定义如下表,其中CE#和R/B#分别有两个引脚,分别对应两个die:

1.5 双平面(plane)操作

每个NAND闪存逻辑单元(LUN)被划分为多个物理平面。每个平面包含独立于其他平面的高速缓存寄存器和数据寄存器。这些平面通过低位的块地址位寻址。如存储结构图中的Note所示。

双平面操作通过在多个平面上执行并发的读取、编程或擦除操作,更好地利用了这些物理平面上的NAND闪存阵列,显著提高了系统性能。两个平面之间的操作必须是相同类型的;例如,不能在一个平面上执行PROGRAM操作而在另一平面上执行ERASE操作。

当发出双平面编程或擦除操作时,使用READ STATUS(70h)命令并检查先前的操作是否失败。如果READ STATUS(70h)命令指示发生错误(FAIL=1和/或FAILC=1),则使用READ STAUTS ENHANCED(78h)命令确定哪个平面操作失败。

1.6 Die间交错操作

在有多个die的芯片中,可以通过die间交错操作提升性能。交错操作是在一个die繁忙(RDY=0)时向空闲die(RDY=1)发出的操作。但在RESET(FFh)、读标识(90h、ECh、EDh)和特性配置(EEh、EFh)操作之后,直到目标上所有die的ARDY=1之前,禁止多die交错操作。

在交错操作期间,有两种方法可以确定操作是否完成。R/B#信号指示对应die何时完成其操作。当任何die忙时,R/B#保持为低。当R/B#变高时,对应die处于空闲状态,操作完成。或者,也可以通过READ STATUS ENHANCED(78h)命令单独报告每个die的状态。

如果裸片(LUN)正在执行高速缓存操作,如页高速缓存编程(80h-15h),则当状态寄存器位6为1时(RDY=1),裸片(LUN)能够接受另一高速缓存操作的数据。所有操作(包括高速缓存操作)在状态寄存器位5为1时(ARDY=1)在裸片上完成。

1.7 错误管理

通常Nand Flash出厂时就有可能存在缺陷,同时这种缺陷会影响块擦除,这样的缺陷被称为坏块。所以这时就需要坏块管理和纠错算法来保证数据的完整性。

每个block的第一个(规范规定可以是第一个也可以是最后一个)page中有64字节的spare area,可用来标记坏块。如果一个块是有缺陷的,并且使用 8-bit 数据访问方式,则制造商应该通过设置有缺陷的块的第一个(或者最后一个)page 中,缺陷区域(这个缺陷区域规范中没有明确是什么地址)的第一个Byte 为00h,来标记有缺陷的块。如果一个块是有缺陷的并且使用16-bit数据访问方式,则通过设置缺陷块的第一个(或最后一个)page 中,缺陷区域的第一个word 为 0000h,来标记有缺陷的块。

主机软件在对nand flash进行编程或擦除前,应先到每个block的第一个page First spare area location进行检查,判断哪些block是坏块,然后生成一张坏块表。

为了保证数据的完整性,建议做如下操作:

1、在编程和擦除操作后检查状态;

2、在典型场景下,使用最小ECC要求;

3、使用坏块管理机制和磨损均衡算法;

| Description | Requirement |

| Minimum number of valid blocks (NVB) per LUN | 4016(出厂时好块不能低于4016) |

| Total available blocks per LUN | 4096 |

| First spare area location | x8: byte 2048 |

| Bad-block mark | x8: 00h |

| Minimum required ECC | 4-bit ECC per 528 bytes |

| Minimum ECC with internal ECC enabled | 4-bit ECC per 516 bytes (user data) + 8 bytes (parity data) |

| Minimum required ECC for block 0 if PROGRAM/ERASE cycles are less than 1000 | 1-bit ECC per 528 bytes |

芯片的大致功能介绍到这里,下一讲分享部分重要的操作指令,敬请期待!

上一篇:遨博机械臂——末端工具ROS驱动

下一篇:智慧图书馆解决方案-最新全套文件